Charge Trapping Related Degradation of Thin HfAlO/SiO<sub>2</sub> Gate Dielectric Stack during Constant-Voltage Stress

Piyas Samanta,<sup>a,z</sup> Chin-Lung Cheng,<sup>b,\*,z</sup> and Yao-Jen Lee<sup>c</sup>

<sup>a</sup>Department of Physics, Vidyasagar College for Women, Kolkata 700 006, India <sup>b</sup>Institute of Mechanical and Electro-Mechanical Engineering, National Formosa University, Yunlin 63201, Taiwan

<sup>c</sup>National Nano Device Laboratories, Hsinchu 30078, Taiwan

Charge carrier generation/trapping and the related degradation of a thin HfAlO/SiO2 stack in n-type metal-oxide-semiconductor capacitors have been investigated under constant gate voltage stress. The results show that dielectric degradation is a composite effect of neutral trap creation, surface state generation at the Si/SiO2 interface, and positive charge trapping in the bulk. The neutral traps created during stress are homogeneously distributed across the oxide following Poisson's random statistics. A significant amount of border-trapped charges was observed in both as-deposited and poststressed devices. The kinetics of generation of both oxide-trapped positive charges and interface trapped charges are found to be similar. Both these defects are possibly created by the hydrogen-related species. We demonstrate that compared to HfO<sub>2</sub> devices, HfAlO devices with an equal equivalent oxide thickness (EOT) show better performances in memory and logic applications. On the contrary, at a given stress voltage, the threshold voltage degradation  $\Delta V_{\rm T}$  and stress-induced leakage current degradation in HfAlO samples are larger, indicating a shorter device lifetime compared to the HfO<sub>2</sub> samples of the same EOT. © 2009 The Electrochemical Society. [DOI: 10.1149/1.3148203] All rights reserved.

Manuscript submitted March 23, 2009; revised manuscript received May 8, 2009. Published June 18, 2009.

Scaling down the conventional silicon dioxide (SiO<sub>2</sub>) film thickness below  $\sim 2$  nm in complementary metal oxide semiconductor (CMOS) devices leads to excessive leakage current due to the direct tunneling of electrons between the electrodes and device reliability problems. To provide sufficient gate control with reduced gate leakage current, alternative high-k dielectrics having a permittivity higher than SiO<sub>2</sub> are being extensively investigated for future generation CMOS devices.<sup>1-17</sup> Among the various high- $\kappa$  dielectrics being studied, hafnium oxide (HfO<sub>2</sub>) has emerged as the most promising candidate due to its relatively high dielectric constant (  $\sim$  22), large bandgap (  $\sim$  5.25 eV), large conduction- and valence-band offsets, and compatibility with the polysilicon gate process.<sup>2,7,17</sup> However, the major drawback of  $HfO_2$  is that pure as-deposited amorphous HfO2 crystallizes<sup>6,7</sup> at 400-450°C, resulting in a large leakage current and the paths for oxygen or dopant diffusion in the dielectric via grain boundaries, threshold voltage instability, and defect generation.<sup>7,8</sup> Recently, Zhu et al.<sup>6</sup> showed that alloying of HfO2 and Al2O3 increases the crystallization temperature up to 1000°C compatible with the thermal budget in standard CMOS process. In the past few years, considerable progress has been made in understanding the effect of aluminum inclusion on electrical and material properties of hafnium aluminate (HfAlO) films.<sup>6-10</sup> However, little work<sup>11,12</sup> has been done in assessing the reliability of HfAlO films with a tantalum nitride (TaN) gate. We therefore attempt to investigate charge-carrier generation/trapping in HfAlO dielectrics during constant voltage stress (CVS) to gain better physical insights into the generation mechanism of oxide charges.

## Experimental

Following the standard RCA cleaning process, (100)-oriented boron-doped p-type Si wafer of 15–25  $\Omega$  cm resistivity was thermally oxidized in dry oxygen at 800°C to form an interfacial SiO<sub>2</sub> 2 nm thick as measured by spectroscopic ellipsometry. A 2 nm thick HfAlO film was deposited on the SiO<sub>2</sub> layer using atomic layer deposition from a HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> combination with a 1:1 weight ratio. After formation of the gate stack, a 100 nm thick TaN metal gate was deposited by reactive sputtering on top of the high-k layer. All n-type metal-oxide-semiconductor (nMOS) capacitors received postmetallization rapid thermal annealing at 750°C in N2 gas for

30 s and back side aluminum deposition for ohmic contact. Several identical test capacitors with gate areas of  $150 \times 150$ ,  $100 \times 100$ , and 50  $\times$  50  $\mu m$  were used in this study. Devices were subjected to dc CVS under negative bias on the TaN gate, keeping the p-type Si in accumulation. Stressing and sensing measurements were done on several identical test structures at room temperature in a darkshielded chamber using a Keithley 4200 semiconductor characterization system (SCS) and Keithley 236 source measure units. Capacitance-voltage (C-V) measurements were done using an Agilent 4284A precision LCR meter controlled by SCS via a Keithley 708A switching matrix.

The flatband voltage  $(V_{\text{FB}})$ , midgap voltage  $(V_{\text{mg}})$ , and the channel threshold voltage  $(V_{\rm T})$  were estimated utilizing the measured high frequency (100 kHz) C-V data (swept from inversion to accumulation) and theoretical simulation incorporating the quantum mechanical (QM) effect including the wave function penetration in SiO<sub>2</sub>.<sup>18</sup> From QM simulation, the extracted equivalent oxide thickness (EOT) of the stack was  $\approx 2.63$  nm (within 5% variation in several devices). The capacitance equivalent thickness extracted from the measured capacitance in accumulation was  $\approx 2.83$  nm. The calculated dielectric constant of the deposited HfAlO was about 12.4.

## **Results and Discussion**

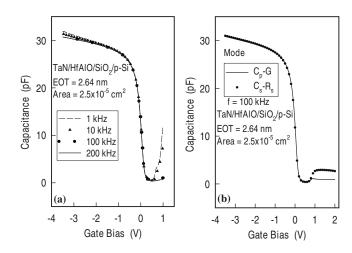

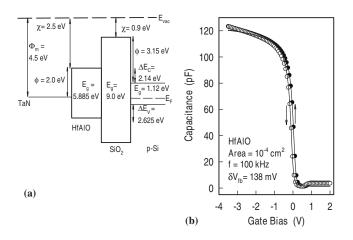

Device characterization.— The measured C-V characteristics with as-deposited HfAlO films exhibit a good saturation behavior in accumulation of p-Si at the ac signal frequencies in the range between 1 and 200 kHz, as shown in Fig. 1a. In Fig. 1a the frequency dispersion in the effective dielectric constant of the HfAlO stack was insignificant, indicating a low series resistance associated with the device structure. This is further supported by the identical values of the capacitances measured in the accumulation regime in both series and parallel mode at a given bias and frequency, as depicted in Fig. 1b. Therefore, hereafter in assessing the dielectric quality during stress, the C-V curves were measured in parallel mode at an ac signal frequency of 100 kHz. A low series resistance of the device structure was achieved due to the ohmic contact of the back side of the wafer. The energy band diagram of the nMOS capacitors with a HfAlO/SiO<sub>2</sub> stack is shown in Fig. 2a taking the work function of TaN on HfAlO as 4.5 eV.<sup>12</sup> The important energy parameters, viz., conduction- and valence-band offsets, bandgap of HfAlO as depicted in Fig. 2a, were estimated according to the prescriptions by Yu et al.<sup>17</sup> and taking mole fraction of HfO<sub>2</sub> in  $(HfO_2)_x (Al_2O_3)_{1-x}$ as 0.5.

<sup>\*</sup> Electrochemical Society Active Member.

<sup>&</sup>lt;sup>z</sup> E-mail: piyas\_samanta@yahoo.com; chengcl@nfu.edu.tw

**Figure 1.** (a) A typical multifrequency capacitance–voltage (C-V) plot of an nMOS capacitor with a HfAlO/SiO<sub>2</sub> gate stack. (b) C-V plot of a HfAlO MOS capacitor in series and parallel modes at an ac signal frequency of 100 kHz. All measurements were recorded by sweeping the gate bias from inversion to accumulation of the p-Si.

From the full QM simulation of the measured C-V results, the estimated  $V_{\rm FB}$  of the as-fabricated capacitors was  $\approx +0.19$  V. The positive  $V_{\rm FB}$  caused due to incorporation of Al into HfO<sub>2</sub> was also reported by several researchers.<sup>7,9</sup> Considering the work function difference between the p-type Si substrate and TaN metal gate,  $V_{\rm FB}$ should be about -0.25 V. Consequently, negative fixed charges were present in the HfAlO/SiO<sub>2</sub> stack and its density was estimated to be about  $3.5 \times 10^{12}$  cm<sup>-2</sup>. As-fabricated HfAlO capacitors exhibit a significant hysteresis during double-bias sweep measurement, as depicted in Fig. 2b. About 138 mV of negative  $V_{\rm FB}$  shift was observed after the second sweep, i.e., when going back to inversion from accumulation, as illustrated in Fig. 2b. We believe that the C-Vhysteresis in the metal-oxide-semiconductor (MOS) capacitor is attributed to electron charging and discharging by direct tunneling through the ultrathin SiO<sub>2</sub> to the substrate. From the above value of  $V_{\rm FB}$  shift, the effective density of detrapped electrons was found to be about  $1.1 \times 10^{12} \text{ cm}^{-2}$ .

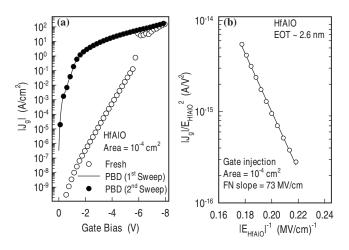

Figure 3a shows the tunneling current density  $J_g$  as a function of applied gate bias keeping p-Si in accumulation. Multiple breakdowns were not observed in the HfAlO devices up to the voltage

**Figure 2.** (a) Schematic energy band diagram of nMOS capacitor with  $HfAlO/SiO_2$  stack. (b) Bidirectional HFCV characteristics of a virgin nMOS capacitor with a  $HfAlO/SiO_2$  stack dielectric. Data were recorded from inversion to accumulation (solid circles) and back to inversion (open circles). Solid lines are from QM simulation.

**Figure 3.** Absolute magnitude of gate tunneling current density  $J_g$  as a function of (a) applied gate bias and (b) electric field across the HfAlO layer.

range studied here. The overlapping of the postbreakdown sweep *J-V* characteristics in Fig. 3a indicates hard breakdown. At an electric field  $E_{\rm hk}$  above 4 MV/cm in the HfAlO layer and before dielectric breakdown, the current through the HfAlO layer is due to Fowler–Nordheim (FN) tunneling,<sup>19</sup> as seen from the straight-line fit to  $\ln(J_g/E_{\rm hk}^2)$  vs  $1/E_{\rm hk}$  plot of the measurement results illustrated in Fig. 3b. The FN slope during gate injection in as-fabricated HfAlO devices was 73 MV/cm as estimated from numerical fit of the measured data with the well-known FN equation<sup>19</sup> given by

$$J_{\rm FN} = A_{\rm FN} E_{\rm hk}^2 \exp(-B_{\rm FN}/E_{\rm hk})$$

[1]

where  $A_{FN}$  and  $B_{FN}$  are constants and  $E_{hk}$  is the electric field across the HfAlO layer as calculated from

$$E_{\rm hk} = \frac{V_{\rm hk}}{T_{\rm hk}} = \frac{V_{\rm di}}{T_{\rm hk} + \left(\frac{\varepsilon_{\rm hk}}{\varepsilon_{\rm ox}}\right)T_{\rm ox}}$$

[2a]

$$V_{\rm di} = V_{\rm g} - V_{\rm FB} - \psi_{\rm Si}$$

[2b]

where  $V_{\rm hk}$  is the voltage drop in the high- $\kappa$  layer,  $T_{\rm ox}$  and  $T_{\rm hk}$  are the physical thicknesses of SiO<sub>2</sub> (permittivity  $\varepsilon_{\rm ox}$ ) and high- $\kappa$  dielectric (permittivity  $\varepsilon_{\rm hk}$ ), respectively, and  $V_{\rm di}$  is the voltage drop across the dielectric stack.  $V_{\rm g}$ ,  $V_{\rm FB}$ , and  $\psi_{\rm Si}$  are the gate voltage, flatband voltage, and surface potential in silicon, respectively.

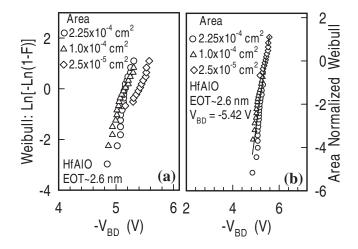

To study the wafer level reliability, we have performed the ramped voltage stress (RVS) measurement with a step size of 0.03 V corresponding to a linear voltage ramp rate of about 0.75 MV/cm s in several identical capacitors of various gate areas. The statistics of dielectric breakdown voltage  $V_{\rm BD}$  obeys the Weibull distribution given by

$$F(V_{\rm BD}) = 1 - \exp\left\{-\left(\frac{V_{\rm BD}}{\alpha}\right)^{\beta}\right\}$$

[3]

where *F* is the cumulative failure probability,  $V_{\rm BD}$  is the random variable for breakdown voltage,  $\alpha$  is the breakdown voltage at the failure percentage of 63.2%, and  $\beta$  is the shape factor or Weibull slope. In Fig. 4a, the time-zero dielectric breakdown voltage ( $V_{\rm BD}$ ) distributions are shown for various capacitor sizes. The gate voltages to breakdown  $V_{\rm g,BD}$  were taken from the sweep *I-V* characteristics during RVS. Using Eq. 2b,  $V_{\rm BD}$  was estimated from the measured values of  $V_{\rm g,BD}$ ,  $V_{\rm FB}$ , and  $\phi_{\rm Si}$  of each individual capacitor. If the breakdown distributions follow Poisson's random statistics, we have<sup>20</sup>

Figure 4. (a) Individual Weibull distributions of breakdown voltage  $V_{\rm BD}$  of HfAlO capacitors for different areas. (b) Normalized Weibull plot of  $V_{\rm BD}$  with the identical data from (a) by using Eq. 4 at a reference area of 2.5  $\times 10^{-5}$  cm<sup>2</sup>. Line is the fit to Weibull statistics. The dielectric breakdown voltage at 63.2% of failure percentile was estimated at 5.42 V.

$$\ln\{-\ln[1 - F(V_{BD1})]\} - \ln\{-\ln[1 - F(V_{BD2})]\} = \ln\left(\frac{S_1}{S_2}\right) \quad [4]$$

where  $V_{\rm BD1}$  and  $V_{\rm BD2}$  are the dielectric voltages to breakdown for capacitors with areas  $S_1$  and  $S_2$ , respectively. Figure 4b shows areascaled Weibull  $W \equiv \ln[-\ln(1 - F)]$ , where the individual  $V_{BD}$  distributions for different gate areas are normalized to 2.5 imes 10<sup>-5</sup> cm<sup>2</sup> using Eq. 4. In Fig. 4b the normalized V<sub>BD</sub> distributions of various capacitor areas merge to a single Weibull breakdown distribution, indicating<sup>20</sup> that the defect-related dielectric breakdown is intrinsic and can be explained by the precolation model.<sup>21</sup> Furthermore, the overlap of the area-scaled Weibulls of capacitors of various sizes, as shown in Fig. 4b, reveals that the defects in the dielectric are homogeneously distributed across the oxide area following Poisson random statistics.<sup>20</sup> From the merged Weibull distribution of  $V_{\rm BD}$ , the estimated dielectric breakdown voltage at 63.2% failure percentile was -5.42 V which corresponds to 20.6 and  $6.5 \; MV/cm$  of the electric fields across the interfacial  $\mathrm{SiO}_2$  and HfAlO layers, respectively.

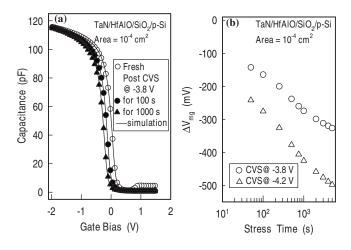

Charge carrier trapping.— To study the stress-induced charge generation/trapping in the gate stack, high frequency capacitance–voltage (HFCV) measurements were performed before and after CVS. In our devices, HFCV curves shifted toward more negative voltage after CVS, as depicted in Fig. 5a, indicating positive charge buildup<sup>22</sup> in the gate dielectric. Positive oxide charge trapping was further confirmed (Fig. 5b) from the negative shift  $\Delta V_{mg}$  of the midgap voltage after electrical stress relative to the fresh device following the relationship<sup>2,14</sup>

$$\Delta N_{\rm ot} = -\frac{\Delta V_{\rm mg} \varepsilon_{\rm ox}}{q T_{\rm eq}}$$

[5]

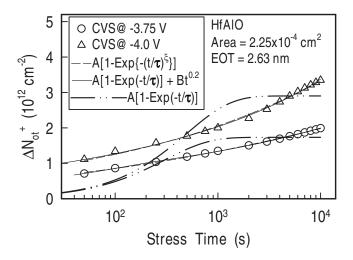

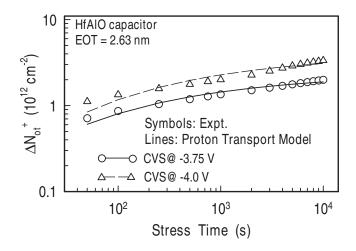

where *q* is the magnitude of electronic charge,  $T_{eq}$  is the EOT of the gate stack, and  $\Delta N_{ot}$  is the variation in the density of stress-induced oxide-trapped charges. The variations in the density of stress-induced oxide-trapped positive charges  $\Delta N_{ot}^+$  are shown in Fig. 6 as a function of stress time during CVS at various stress voltages. *C-V* measurement is sensitive to the charges trapped closer to the Si/SiO<sub>2</sub> interface.<sup>22</sup> Consequently, the positive oxide charge is located close to the Si/SiO<sub>2</sub> interface.<sup>13</sup>

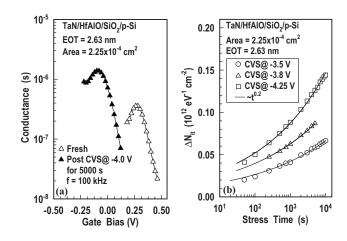

The change in the conductance peak value after CVS relative to the virgin device shown in Fig. 7a indicates interface state  $D_{it}$  generation during stress.<sup>22</sup> Estimated midgap surface state density  $D_{it}$  in

**Figure 5.** (a) HFCV characteristics of an nMOS capacitor with a HfAlO/SiO<sub>2</sub> stack dielectric measured before and after CVS at -3.8 V for different times. Solid lines are from QM simulation.<sup>16</sup> (b) Stress time dependence of midgap voltage shift during CVS with stress voltage  $V_g^{\text{stress}}$  as a parameter. Solid lines are from power-law fit.

as-fabricated devices was  $(2-3) \times 10^{10} \text{ cm}^{-2} \text{ eV}^{-1}$ . The instantaneous value of  $D_{\text{it}}$  was calculated from the single high frequency (100 kHz) *C-V* and *G-V* data according to<sup>23</sup>

$$D_{\rm it} = \left\{ \frac{2(G_{\rm m,max}/\omega)}{qS} \right\} \left[ \left( \frac{G_{\rm m,max}}{\omega C_{\rm ox}} \right)^2 + \left( 1 - \frac{C_{\rm m}}{C_{\rm ox}} \right)^2 \right]^{-1} \qquad [6]$$

where  $G_{\rm m,max}$  is the maximum ac conductance with its corresponding capacitance  $C_{\rm m}$ ,  $C_{\rm ox}$  is the oxide capacitance as measured from the QM simulation,<sup>18</sup> and S and  $\omega$  are the capacitor area and ac signal frequency in rad/s, respectively. Figure 7b shows the variation in the density of stress-induced interface states  $\Delta D_{\rm it}$  at various values of  $V_{\rm g}^{\rm stress}$ . Similar to the oxide-trapped positive charges, interface state generation is accelerated with increasing  $V_{\rm g}^{\rm stress}$ , which in turn is related to the electron energy reaching the anode.

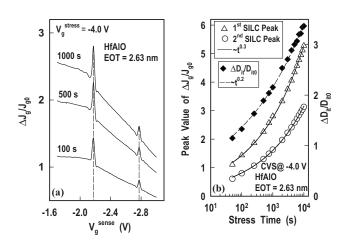

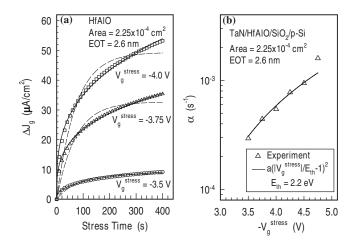

*SILC.*— The gate current density at a given sensing gate voltage  $V_g^{\text{sense}}$  increases after CVS. This increase  $\Delta J_g$  in gate current from its prestress value  $J_{g0}$  is called the stress-induced leakage current (SILC) and is often described by the "normalized SILC" defined as  $\Delta J_g/J_{g0}$ . Figure 8a is a typical plot showing the normalized SILC

**Figure 6.** Variation in the density of oxide-trapped positive charges  $\Delta N_{ot}^{+}$  with stress time during CVS at different voltages. Symbols are from experiment. Curves are fits to various theoretical models.

**Figure 7.** (a) High frequency conductance–voltage characteristics (parallel mode) of an nMOS capacitor with a HfAlO/SiO<sub>2</sub> stack dielectric measured before and after CVS at -4.0 V for 5000 s. (b) Variation in the density of surface states  $\Delta D_{it}$  with stress time during CVS at different voltages. Symbols are from experiment. Curves are from power-law fits.

spectra measured immediately after CVS at -4.0 V for different times. The normalized SILC spectra show two distinct peaks at  $V_{\sigma}^{\text{sense}} = -2.175$  and -2.625 V, indicating two distinct conducting paths. To explain the SILC conduction mechanism, Ghetti et al. proposed trap-assisted tunneling (TAT) via surface states in control oxide devices. However, although a significant amount of interface states is generated during CVS, TAT via surface states cannot explain the observed SILC in our HfAlO devices as explained below. First, TAT via D<sub>it</sub> to be the conduction mechanism of SILC, normalized SILC at a given  $V_{g}^{\text{sense}}$ , should exhibit a proportionality to the surface state density  $D_{it}$  as proposed by Ghetti et al.<sup>24</sup> However, no proportionality between either of the two peak values in the normalized SILC spectrum and  $D_{it}$  is observed in our devices, as demonstrated in Fig. 8b. Second, stress-induced interface traps are the trivalent Si<sub>3</sub>  $\equiv$  Si<sup>\*</sup> dangling bonds, so-called  $P_{b0}$  centers<sup>4</sup> exhibiting U-shaped distribution<sup>22</sup> in the 1.12 eV bandgap of Si. Therefore, for TAT via interface states to be a possible mechanism of SILC, the normalized SILC spectrum should exhibit several peaks contrary to the observed two peaks shown in Fig. 8a. In view of the above, we

**Figure 8.** (a) Normalized SILC measured after CVS at -4.0 V for different times as a function of gate sensing voltage in an nMOS capacitor with HfAIO/SiO<sub>2</sub> gate stack. (b) Plot of two peaks in the normalized SILC spectrum (open symbols) measured after CVS at -4.0 V (left *y*-axis) and generated surface state density normalized to its initial value  $D_{it0}$  (filled symbols) (right *y*-axis) as a function of injected electron fluence  $Q_{inj}$ . Curves are from power-law fits.

**Figure 9.** (a) Stress time dependence of the increase in absolute magnitude of tunneling current density  $J_g$  relative to the fresh device observed during CVS with stress voltage as a parameter. Solid and dashed lines are fits to Eq. 7 and the first term on right side of Eq. 7, respectively. (b) Normalized trap generation rate per injected electron as a function of stress voltage in a MOS capacitor with a HfAlO/SiO<sub>2</sub> stack. Solid line is fit to Eq. 8.

propose that stress-induced interface traps do not play a role in the SILC observed beyond  $V_{\rm FB}$  through the HfAlO stack deposited on nondegenerately doped Si, contrary to the article<sup>24</sup> dealing in devices on heavily doped Si.

Stress-induced neutral trap creation in our devices is evident from the nonsaturating behavior of the time evolution of  $J_g$  during CVS for different stress voltages, as depicted in Fig. 9a. The nonsaturating behavior of  $J_g$  was also observed at a longer stress time up to 10,000 s. This increase in  $J_g$  could be due to the enhanced electric field at the cathode (TaN gate) due to the trapped positive oxide charge and/or due to the TAT.<sup>25</sup> Therefore, the increment  $\Delta J_g(t)$  in  $J_g$  during CVS can be modeled by<sup>3,5</sup>

$$\Delta J_{\rm g} = A \left[ 1 - \exp\left(-\frac{t}{\tau}\right) \right] + Bt^{\delta}$$

<sup>[7]</sup>

where A and  $\tau$  are constants,  $\delta$  is a fraction depending on the charge state and atomicity of hydrogen during transport, and B is the trap generation rate during CVS and is a function of electronic energy. The first term on the right side of Eq. 7 takes into account the effect of oxide charge buildup, while the second term takes care of the SILC contribution via TAT. The first term alone cannot explain the observed  $\Delta J_g - t$  variations in either of the devices, as evident from the dashed lines in Fig. 9a. Therefore, the increase in  $J_{\rm g}$  is less sensitive to the positive charge buildup in the dielectric. Rather, the time evolution ( $t^{0.3}$  dependence) of  $J_g$  during CVS can be best explained by the composite effects of the above two mechanisms (solid lines), as illustrated in Fig. 9a. Neutral electron trap creation rate per injected electron in HfAlO capacitors is also shown in Fig. 9b as a function of absolute magnitude of applied gate voltage during CVS. The normalized value of the trap creation rate is  $Bt_{\text{stress}}^{\delta}/Q_{\text{inj}}$ , where  $t_{\text{stress}}$  is the total stress time at which the gate voltage is interrupted<sup>3</sup> and  $Q_{\text{inj}}$  is the injected electron flux during the electrical stress. Evidently trap creation rate  $dN_t/dt$  follows<sup>5</sup>

$$\frac{dN_t}{dt} = C \left(\frac{|V_{\rm g}^{\rm stress}|}{E_{\rm th}} - 1\right)^2$$

[8]

where C is a constant and  $E_{\text{th}}$  is the threshold voltage for trap creation. The estimated value of  $E_{\text{th}}$  in HfAlO dielectric was found 2.2 eV.

*Mechanism of charge carrier generation.*— The origin of positive oxide charge in a hafnium-based gate stack remains controversial between trapping of holes<sup>11,12,26,27</sup> and protons.<sup>3-5</sup> The above

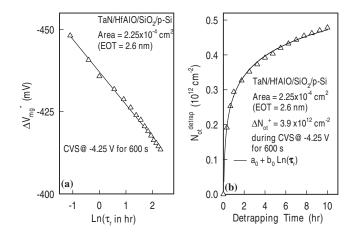

**Figure 10.** (a) Measured midgap voltage shift  $\Delta V_{mg}^*$  due to detrapping of oxide positive charges at room temperature as a function of logarithmic time  $\tau_r$ . Oxide positive charges were trapped at room temperature during CVS at -4.25 V for 600 s. (b) Density of detrapped oxide positive charge observed at room temperature as a function of detrapping time  $\tau_r$ . Zero-field emission of oxide charge was measured (symbols) after CVS at -4.25 V for 600 s at room temperature. Curve is from logarithmic fit.

controversy is resolved in this section as follows. Zero-field detrapping of oxide-trapped positive charge is studied, as illustrated in Fig. 10. The straight-line nature of the midgap voltage shift  $\Delta V_{\rm mg}^*$  because of self-detrapping vs logarithmic relaxation time  $\tau_{\rm r}$ , as shown in Fig. 10a, indicates the existence of tunnel detrapping<sup>28</sup> of bulk positive oxide charges at room temperature. Tunnel detrapping of proton-induced defects is not physically acceptable, rather it is conformity with holes from as-fabricated traps.<sup>14</sup> Therefore, hole trapping might explain the oxide positive charge buildup in both devices. A plot of the instantaneous zero-field emission rate of  $N_{\rm ot}^+$  vs reciprocal of detrapping time  $\tau_{\rm r}$  yielded a straight line, as evident from Fig. 10b. This means that intrinsic hole traps in the dielectric stacks are uniformly distributed  $[D_{\rm ox}(E) = {\rm const}]$  in energy<sup>28</sup> in accordance with

$$\frac{dN_{\rm ot}^+}{dt} = \frac{k_{\rm B}TD_{\rm ox}(E)}{t}$$

[9]

where  $N_{ot}^{+}$  is the area density of detrapped positive oxide charge with density of states  $D_{ox}(E)$  in cm<sup>-2</sup> eV<sup>-1</sup>,  $k_{\rm B}T$  is the thermal energy in eV, and t is the detrapping or relaxation time. The constant density of states suggests that the as-fabricated hole traps have a single time constant<sup>28</sup> and therefore can be characterized by a single capture cross section. Our analysis contradicts the observations by Gusev and D'Emic.<sup>29</sup> We explain this in the following way. In their work, the interfacial dielectric was ultrathin silicon oxynitride instead of thermal SiO<sub>2</sub> used in our measurements and the interfacial dielectric plays the role in positive charge and/or hole trapping. Using Eq. 9, the estimated depth of the intrinsic hole traps from the SiO<sub>2</sub> valence bandedge was  $\approx 1.2$  eV. This value is close to that reported for intrinsic hole traps in pure SiO<sub>2</sub> devices.<sup>28</sup>

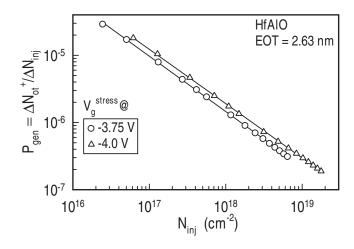

The origin of trapped holes in the dielectric during negative-bias CVS may be either valence band tunneling (VBT)<sup>27,30</sup> or anode hole injection (AHI).<sup>30,31</sup> For the VBT mechanism of holes, the oxide positive charge generation probability  $P_{gen} = \Delta N_{ot}^+/\Delta N_{inj}$  should not depend on stress voltage. This is because of filling of the preexisting hole traps.  $P_{gen}$  is also shown in Fig. 11 as a function of the injected electron density  $N_{inj}$  during the negative-bias CVS in both capacitors. As evident in Fig. 11, irrespective of the dielectric stacks,  $P_{gen}$  strongly depends on  $V_g^{stress}$ , which in turn is related to the electron energy reaching the anode. Moreover, for VBT to be a possible mechanism, trapped oxide positive charge buildup should saturate during stress consistent with the filling of pre-existing traps. How-

Figure 11. Oxide positive charge trapping probability as a function of number of injected electrons into  $HfAlO/SiO_2$  stack during negative-bias CVS with stress voltage as a parameter.

ever, no such saturation in oxide positive charge buildup was observed in either of the devices within the stress time shown in Fig. 6. On the contrary,  $\Delta N_{ot}^{+}$  monotonically increases with stress time, indicating generation of defects in the dielectric during stress. Therefore, hole trapping via a VBT mechanism during negative-bias CVS seems unlikely in these devices. To model the positive charge buildup in high-k stacks due to hole trapping, the stretchedexponential  $A\{1 - \exp[-(t/\tau)^{\xi}]\}$  formalism has been made popular by several researchers.<sup>26,27</sup> Stress time dependence of  $\Delta N_{ot}^+$  can be mathematically well reproduced by the stretched exponential with distribution width  $\zeta \approx 0.22$ , as shown by the filled dots in Fig. 6. However, the stretched-exponential formulation (with  $\beta < 1$ ) is based on the a priori assumption of continuous distribution of cap-ture cross section of the intrinsic hole traps<sup>26,27</sup> contrary to the single time constant, as determined experimentally in Fig. 10b. Further-more, the distributed capture cross-section model<sup>26</sup> assumes only trap filling without creating additional traps. In view of the above, the distributed capture cross-section  $model^{26,27}$  is not physically viable to explain the positive charge buildup during CVS in either of the high-κ gate stacks studied here.

Hole trapping into as-fabricated hole traps of single capture cross section obeys the simple charging equation<sup>31</sup>  $p(t) = A[1 - \exp(-t/\tau)]$ . However, the estimated oxide positive charge density  $\Delta N_{ot}^{+}$  in either of the devices does not fit with above hole-trapping dynamics, as depicted by the dashed lines in Fig. 6. Rather,  $\Delta N_{ot}^{+}(t)$  fits well (the solid lines in Fig. 6) with

$$\Delta N_{\rm ot}^{+} = A [1 - \exp(-t/\tau)] + B t^{n}$$

[10]

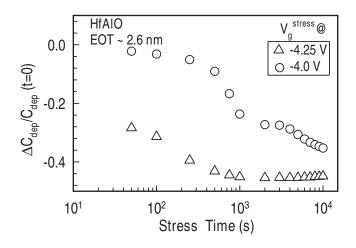

The first term on the right side of Eq. 10 is due to hole trapping in pre-existing neutral traps via AHI, while the second term is due to defect generation. The power-law exponent  $n \approx 0.2$  in Eq. 10 reproduces  $\Delta N_{\text{ot}}^{\dagger}$  during CVS, as depicted in Fig. 6.  $\delta \approx 0.2$  is consistent with the dispersive transport of proton through the interfacial  $SiO_2$  during negative-bias stress in the stack.<sup>32</sup> Furthermore, the maximum depletion capacitance is observed to decrease during CVS of the capacitors, as depicted in Fig. 12. This decrease can be attributed to the reduction in the density of active boron acceptor impurities in the p-type Si substrate, resulting from the formation of B-H Such complexes are induced by the transport of hydrocomplexes. gen in the Si substrate, consistent with the picture involving the release of hydrogen during CVS. We therefore propose that bulk oxide positive charges in the HfAlO dielectric stack are attributed to holes and proton-induced defects. However, the contribution of proton-related defects is significantly larger than that of holes in oxide positive charge buildup. Recently, from the bias temperature

**Figure 12.** Relative maximum depletion capacitance  $[C_{dep} - C_{dep}(0)]/C_{dep}(0)$  of an nMOS capacitor as a function of stress time during CVS.

stress measurements in HfO<sub>2</sub> and SiO<sub>2</sub> devices, we have identified these proton-related defects as the overcoordinated  $[Si_2 = OH]^+$  centers.<sup>13</sup> Both  $\Delta N_{ot}^+$  and  $\Delta D_{it}$  follow a  $t^n$  ( $n \approx 0.2$ ) power law for both devices (Fig. 6 and 7), indicating the similar generation kinetics for these two types of defects.<sup>14</sup>

*Model.*— During negative-bias stress, the injected electrons are transported toward the Si/SiO<sub>2</sub> interface (anode) under the electric field in the dielectric stack. These electrons acquiring energy above the threshold energy for the liberation of hydrogen (proton) at the Si/SiO<sub>2</sub> interface depassivate Si<sub>3</sub>  $\equiv$  SiH centers, leading to the generation of trivalent Si<sub>3</sub>  $\equiv$  Si\* dangling bonds acting as the interface states and the subsequent release of hydrogen (proton).<sup>4</sup> These liberated protons are then accelerated toward the cathode (TaN gate) under the oxide electric field  $E_{\text{ox}}$ , leading to the breaking of the bridging oxygen bonds and subsequent trapping of H<sup>+</sup> by the strained Si–O–Si bonds<sup>5,13</sup> forming oxide positive charges. A fraction of the liberated hydrogen, while accelerated toward the cathode, generates neutral traps in the high- $\kappa$  layer.<sup>3-5</sup> In the framework of the dispersive proton transport model,<sup>4,28</sup> one can model positive oxide charge buildup by

$$\Delta N_{\text{ot}}^{+}(t) = N_{\text{oxT}} \{1 - \exp[-\sigma(H_{\text{bulk}}^{+})(t)]\}$$

[11a]

$$\left[\mathbf{H}_{\text{bulk}}^{+}\right] = \left[\mathbf{H}_{\text{int}}^{+}\right] \left[1 - \int_{0}^{I(t)} G(y) dy\right]$$

[11b]

$$[H_{int}^{+}] = [Si_3 \equiv SiH][1 - exp(-\sigma_H^{+}N_{inj})]$$

[11c]

where  $N_{\text{oxT}}$  is the total density of strained bonds in the SiO<sub>2</sub> layer,  $\sigma$  is their mean trapping cross section, and  $[\text{H}^+_{\text{bulk}}]$  is the bulk concentration of proton at a time *t* and is related to the instantaneous hydrogen concentration at the interface  $[\text{H}^+_{\text{int}}]$  by the transport equation (Eq. 11b). G(y) is a trial function related to the probability of finding a proton at a given distance from the interface at a given time *t* and  $\ell(t)$  is related to the dispersiveness of proton transport.<sup>34</sup> [Si<sub>3</sub>  $\equiv$  SiH] is the initial concentration of passivated SiH bonds that after depassivation yields H<sup>+</sup> with a liberation cross section  $\sigma_{\text{H}^+}$  and  $N_{\text{inj}}$  is the number of injected electrons per unit area. Figure 13 shows that the above proton transport model can well reproduce the measured density of oxide-trapped positive charges during CVS in HfAIO capacitors.

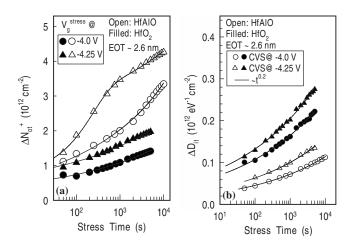

*Comparison between HfAlO and HfO*<sub>2</sub> *devices.*— To compare the carrier trapping related deterioration of the gate stack and device performances, HfAlO and HfO<sub>2</sub> capacitors of equal EOT were used

Figure 13. Variation in trapped oxide positive charge density in HfAlO capacitors with stress time during CVS at various voltages. Symbols are from measurements and curves are from dispersive proton transport model.

here. The process flow of the  $HfO_2$  devices can be found elsewhere.<sup>35</sup> Al incorporation in  $HfO_2$  introduces more oxide fixed charge and border trap in as-fabricated HfAlO samples when compared with the virgin HfO<sub>2</sub> devices of same EOT (not shown here). Like in HfAlO devices, HfO2 devices exhibit positive oxide charge trapping during negative-bias CVS. A relative comparison of oxide positive charge buildup rate in both devices is shown in Fig. 14a at various equal stress voltages. The principle of operation of charge trapping memory devices is closely related to the oxide charge buildup in MOS capacitors.<sup>35</sup> Therefore, the larger value of  $\Delta N_{ot}^{+}$  at a given stress voltage, as depicted in Fig. 14a, indicates better performance of charge trapping memory devices with HfAlO dielectric when compared with HfO<sub>2</sub>/SiO<sub>2</sub> stack of same EOT. Unlike the variation in  $\Delta N_{ot}^{+}$  with stress time during CVS at an identical  $V_{g}^{\text{stress}}$ the amount of  $\Delta D_{it}$  is more in HfO<sub>2</sub> capacitors compared to the HfAlO capacitors, as illustrated in Fig. 14b. Nearly an equal number  $[(2-3) \times 10^{10} \text{ eV}^{-1} \text{ cm}^{-2}]$  of  $D_{it}$  was observed in both asfabricated devices. Results shown in Fig. 14b indicate that addition of Al increases the Si/SiO<sub>2</sub> interface stability in HfAlO devices during CVS. Coulombic scattering due to interface-trapped charges plays a vital role in channel carrier mobility degradation.<sup>36</sup> In view of this, stress-induced channel carrier mobility degradation and

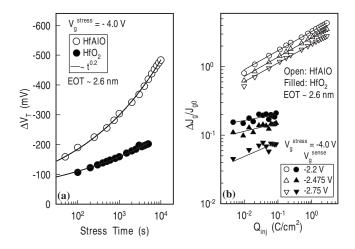

**Figure 14.** Number of stress-induced (a) positive oxide-trapped charges  $\Delta N_{ot}^+$  and (b) interface states  $\Delta D_{it}$  as a function of stress time in HfAlO/SiO<sub>2</sub> (open symbols) and HfO<sub>2</sub>/SiO<sub>2</sub> (solid symbols) stacks during CVS. Results are shown relative to the fresh devices.

**Figure 15.** (a) Threshold voltage shift  $\Delta V_{\rm T}$  relative to the fresh device as a function of stress time and (b) normalized SILC as a function of injected electron fluence Qini in HfAlO/SiO2 (open symbols) and HfO2/SiO2 (solid symbols) stacks after CVS at -4.0 V with sensing voltage  $V_g^{\text{sense}}$  as a parameter.

transconductance  $(g_m)$  degradation in metal oxide semiconducton field-effect transistor (MOSFETs) with HfAlO gate dielectric are lower than that with HfO2 of an equal EOT. Similar observations were experimentally observed by Joo et al.7 in their MOSFET devices.

At a given operating voltage, the higher  $V_{\rm T}$  degradation in HfAlO capacitors, as depicted in Fig. 15a, shortens the device lifetime compared to the devices with HfO<sub>2</sub>/SiO<sub>2</sub> stack of same EOT. In other words, for a given projected lifetime within a given tolerance of  $V_{\rm T}$  shift, the operating voltage of the HfAlO devices would be lower than that of the HfO<sub>2</sub> devices with an identical EOT.  $\Delta V_{\rm T}$  comprises of  $\Delta N_{\rm ot}^+$  and  $\Delta D_{\rm it}^{-35}$  Therefore, comparing the results shown in Fig. 14 and 15a,  $\Delta N_{\rm ot}^+$  significantly contributes in  $V_{\rm T}$  degradation. Similar to  $V_{\rm T}$  degradation, SILC degradation in HfAlO devices is also higher than that of HfO<sub>2</sub> devices of equal EOT, as shown in Fig. 15b. It is discussed above that SILC is due to assisted tunneling via neutral traps generated in the high-k layer during CVS. Therefore, from the results shown in Fig. 15b we propose that at a given  $V_g^{\text{stress}}$ , the neutral trap creation rate is higher in HfAlO devices relative to the HfO2 devices of an equal EOT. Neutral electron traps originated from nonbridging oxygen centers.<sup>8</sup> Al acts as a network modifier<sup>6</sup> by breaking of Al–O–Al bonds which produce nonbridging oxygen centers.<sup>8</sup> Therefore, the higher trap creation in HfAlO stack might be due to larger concentration of nonbridging oxygen centers originated from breaking of Al-O-Al bonds compared to Hf-O-Hf bonds. This argument is further supported from the lower bonding energy of the Al–O bonds (  $\sim 118.5 \text{ eV}$ )<sup>37</sup> than that of the Hf–O bonds (  $\sim 213.1 \text{ eV}$ ).<sup>38</sup> Moreover, gate dielectric breakdown occurs due to the formation of conducting path between the electrodes when the neutral trap density reaches a critical value.<sup>21</sup> In view of this, the results shown in Fig. 15b immediately imply that at a given applied voltage, the dielectric breakdown triggered by neutral trap creation is facilitated in HfAlO capacitors relative to the  $HfO_2$  ones of an equal EOT.

Under negative-bias stress, the stress-induced oxide positive charge buildup is closely related to the electric field  $E_{ox}$  across the 2 nm thick interfacial SiO<sub>2</sub> layer and the trap creation is related to the electric field in the high- $\kappa$  layer in either of the capacitors. For a given  $V_g^{\text{stress}}$ , voltage drop  $V_{\text{ox}}$  across the interfacial SiO<sub>2</sub> in HfAlO capacitors is higher than that in HfO2 capacitors, resulting  $E_{\rm ox}({\rm HfAlO}) > E_{\rm ox}({\rm HfO}_2)$ . Therefore, the density of  $\Delta N_{\rm ot}^+$  is larger in HfAlO capacitors compared to the HfO2 capacitors, as illustrated in Fig. 14a. For a given  $V_{g}^{\text{stress}}$ , voltage drop across the HfAlO layer

is approximately equal to voltage drop across the HfO2 layer, while  $E_{\rm HfAlO} > E_{\rm HfO_2}$  because of the larger physical thickness of the HfO<sub>2</sub> layer. Therefore, at a given stress voltage, neutral trap creation rate in the high- $\kappa$  layer is higher for HfAlO capacitors when compared with HfO<sub>2</sub> capacitors of same EOT.

#### Conclusions

A systematic experimental investigation on the electrical stressinduced degradation of gate dielectrics and device performances with HfAlO gate dielectric is presented. We propose that dielectric degradation is a composite effect of neutral trap creation, surfacestate generation at the Si/SiO2 interface, and positive charge trapping in the bulk. Significant amount of border-trapped charges was observed in both as-deposited and poststressed devices. Similar kinetics of generation of both oxide-trapped charges and interfacetrapped charges was observed. Both these defects are possibly related to hydrogen-related species. Furthermore, the results demonstrate that HfAlO samples are superior to HfO2 samples of equal EOT in charge trapping memory and CMOS logic applications at the cost of shorter device lifetime and enhanced gate dielectric deterioration due to excess oxide charge buildup and neutral trap creation in HfAlO capacitors at a given  $V_{\sigma}^{\text{stress}}$ . The present study gives an important message that bypassing the leakage current benefit due to Al incorporation in HfO<sub>2</sub>, a trade-off between the device performance and dielectric degradation assessing the oxide reliability must be made in selecting the appropriate gate stack of a given EOT.

# Acknowledgment

P.S. thanks Dr. Souvik Mahapatra at Microelectronics Division, IIT, Bombay, for providing the measurement facilities. The authors thank the National Science Council of Taiwan for the financial support under contract no. NSC 97-2221-E-150-072. Technical support from National Nano Device Laboratories (NDL) of Taiwan is also acknowledged.

National Formosa University assisted in meeting the publication costs of this article.

## References

- 1. G. Wilk, R. Wallace, and J. Anthony, J. Appl. Phys., 89, 5243 (2001).

- W. J. Zhu, T. P. Ma, S. Zafar, and T. Tamagawa, IEEE Electron Device Lett., 23, 597 (2002)

- 3. M. Houssa, M. Naili, M. Heyn, and A. Stesmans, Jpn. J. Appl. Phys., Part 1, 40, 2804 (2001).

- M. Houssa, A. Stesmans, R. J. Carter, and M. M. Heyns, Appl. Phys. Lett., 78, 4. 3289 (2001).

- M. Houssa, V. V. Afanasev, A. Stesmans, and M. M. Heyns, Semicond. Sci. Tech-5. nol., 16, L93 (2001).

- W. J. Zhu, T. Tamagawa, M. Gibson, T. Furukawa, and T. P. Ma, IEEE Electron 6. Device Lett., 23, 649 (2002).

- 7. M. S. Joo, B. J. Cho, C. C. Yeo, S. S. Chan, S. J. Whoang, S. Mathew, L. K. Bera, and D. L. Kwong, IEEE Trans. Electron Devices, 50, 2088 (2003). 8.

- S. H. Bae, C. H. Lee, R. Clark, and D. L. Kwong, IEEE Electron Device Lett., 24, 556 (2003). 9. V. Mikhelashvili, B. Meyler, J. Shneider, O. Kreinin, and G. Eisenstein, Microelec-

- tron. Reliab., 45, 933 (2005) O. Buiu, Y. Lu, S. Hall, I. Z. Mitrovic, R. J. Potter, and P. R. Chalker, Thin Solid 10.

- Films, 515, 3772 (2007). 11. W. Y. Loh, B. J. Cho, M. S. Joo, M. F. Li, D. S. Chan, S. Mathew, and D. L.

- Kwong, Tech. Dig. Int. Electron Devices Meet., 2003, 38.3.1.

- W. Y. Loh, B. J. Cho, M. S. Joo, M. F. Li, D. S. Chan, S. Mathew, and D. L. Kwong, IEEE Trans. Device Mater. Reliab., 4, 696 (2004).

- 13. P. Samanta, C. Zhu, and M. Chan, Appl. Phys. Lett., 91, 113516 (2007).

- 14. P. Samanta, C. Zhu, and M. Chan, Microelectron. Eng., 84, 1964 (2007) Y. Zhao, M. Toyama, K. Kita, K. Kyuno, and A. Toriumi, Appl. Phys. Lett., 88, 15.

- 072904 (2006).

- Y. Zhao, K. Kita, K. Kyuno, and A. Toriumi, J. Appl. Phys., 105, 034103 (2009).

- H. Y. Yu, M. F. Li, B. J. Cho, C. C. Yeo, M. S. Joo, D. L. Kwong, J. S. Pan, C. H. Ang, J. Z. Zheng, and S. Ramanathan, *Appl. Phys. Lett.*, **81**, 376 (2002).

- J. R. Hauser and K. Ahmed, AIP Conf. Proc., 449, 235 (1998). 18.

- Z. Weinberg, Solid-State Electron., 20, 11 (1977).

- 20.

- E. Y. Wu and R. P. Vollesrtsen, IEEE Trans. Electron Devices, 49, 2131 (2002).

- J. H. Stathis, J. Appl. Phys., 86, 5757 (1999).

E. H. Nicollian and J. R. Brews, MOS Physics and Technology, Wiley, New York (1982)

- 23. W. A. Hill and C. C. Coleman, Solid-State Electron., 23, 987 (1980).

- 24. A. Ghetti, E. Sangiorgi, J. Bude, T. W. Sorsch, and G. Weber, IEEE Trans. Electron Devices, 47, 2358 (2000).

- D. J. DiMaria and E. Cartier, J. Appl. Phys., 78, 3883 (1995).

S. Zafar, A. Callegari, E. Gusev, and M. V. Fischetti, J. Appl. Phys., 93, 9298 (2003).

- 27. W. Lu, P. Lin, T. Huang, C. Chien, M. Yang, I. Huang, and P. Lehnen, Appl. Phys. Lett., 85, 3525 (2004).

- L. Manchanda, J. Vasi, and A. B. Bhattacharyya, J. Appl. Phys., 52, 4690 (1981).

E. P. Gusev and C. P. D'Emic, Appl. Phys. Lett., 83, 5223 (2003).

P. Samanta, C. L. Cheng, Y. J. Lee, and M. Chan, Microelectron. Eng., 86, 1767 (2020) (2009).

- 31. P. Samanta, Appl. Phys. Lett., 75, 2966 (1999).

- 32. M. A. Alam and S. Mahapatra, Microelectron. Reliab., 45, 71 (2005).

- 33. J. I. Pankove, D. E. Carlson, J. E. Berkeyheiser, and R. O. Wance, Phys. Rev. Lett., 51, 2224 (1983).

- 34. F. B. McLean and G. A. Ausman, Phys. Rev. B, 15, 1052 (1977).

- 35. P. Samanta, Y. J. Lee, C. L. Cheng, and M. Chan, in Proceedings of the International Solid State Device and Materials Conference, Tsukuba, Japan, pp. 354-355 (2008).

- 36. O. Weber, M. Casse, L. Thevenod, F. Ducroquet, T. Ernst, and S. Deleonibus, Solid-State Electron., 50, 626 (2006).

- 37. G. E. McGuire, G. K. Schweitzer, and T. A. Carlson, Inorg. Chem., 12, 2450 (1973).

- 38. B. F. Dzhurinskii, D. Gati, N. P. Sergushin, V. I. Nefedov, and Y. V. Salyn, Russ. J. Inorg. Chem., 20, 2307 (1975).