## Nonvolatile memory with Co – SiO 2 core-shell nanocrystals as charge storage nodes in floating gate

Hai Liu, Domingo A. Ferrer, Fahmida Ferdousi, and Sanjay K. Banerjee

Citation: Applied Physics Letters **95**, 203112 (2009); doi: 10.1063/1.3258471 View online: http://dx.doi.org/10.1063/1.3258471 View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/95/20?ver=pdfcov Published by the AIP Publishing

## Articles you may be interested in

Localized charge trapping and lateral charge diffusion in metal nanocrystal-embedded High-ĸ/SiO2 gate stack Appl. Phys. Lett. **99**, 222102 (2011); 10.1063/1.3664220

Suppression of dielectric crystallization on metal by introduction of SiO2 layer for metal floating gate memory blocking oxide

Appl. Phys. Lett. 99, 222903 (2011); 10.1063/1.3661173

Retraction: "Nonvolatile memory with Co – SiO 2 core-shell nanocrystals as charge storage nodes in floating gate" [Appl. Phys. Lett.95, 203112 (2009)] Appl. Phys. Lett. **96**, 269902 (2010); 10.1063/1.3456728

Formation of Cu nanocrystals on 3-mercaptopropyltrimethoxysilane monolayer by pulsed iodine-assisted chemical vapor deposition for nonvolatile memory applications Appl. Phys. Lett. **94**, 213508 (2009); 10.1063/1.3139072

Nonvolatile nanocrystal charge trap flash memory devices using a micellar route to ordered arrays of cobalt nanocrystals Appl. Phys. Lett. **91**, 153506 (2007); 10.1063/1.2798502

This article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to IP: 137.189.170.231 On: Wed, 24 Dec 2014 02:23:01

## Nonvolatile memory with $Co-SiO_2$ core-shell nanocrystals as charge storage nodes in floating gate

Hai Liu,<sup>a)</sup> Domingo A. Ferrer, Fahmida Ferdousi, and Sanjay K. Banerjee Microelectronics Research Center, R9950, The University of Texas at Austin, Austin, Texas 78758, USA

(Received 10 July 2009; accepted 14 September 2009; published online 18 November 2009)

In this letter, we reported nanocrystal floating gate memory with  $Co-SiO_2$  core-shell nanocrystal charge storage nodes. By using a water-in-oil microemulsion scheme,  $Co-SiO_2$  core-shell nanocrystals were synthesized and closely packed to achieve high density matrix in the floating gate without aggregation. The insulator shell also can help to increase the thermal stability of the nanocrystal metal core during the fabrication process to improve memory performance. © 2009 American Institute of Physics. [doi:10.1063/1.3258471]

The flash memory market has increased very quickly during the past decade. Nanocrystal (NC) floating gate flash memory is considered to be one of the most promising candidates to replace conventional highly doped polysilicon floating gate flash memory widely used in today's commercial market. Using discrete NCs embedded in a dielectric as a floating gate to store charge, lateral charge migration in the floating gate can be dramatically suppressed, making the device more robust against local defects, which can act as a leakage path in the very thin tunneling oxide. Thus smaller memory cell size, better programing/erasing characteristics, and better retention characteristics can be achieved. Since first described by Tiwari et al.,<sup>1</sup> much work has been done in this area to improve NC flash memory device performance. Different materials, such as Si,<sup>2,3</sup> Ge,<sup>4</sup> SiGe,<sup>5</sup> Ni,<sup>6</sup> and Au,<sup>7,8</sup> have been studied to work as the charge storage nodes. To achieve uniformly distributed NC matrix with high density, various NC deposition methods have been employed.<sup>9</sup> However, as the memory cell continuously scales down, there are still big challenges. According to International Technology Roadmap for Semiconductors (ITRS) 2007,<sup>15</sup> the memory cell size will reduce to  $\sim 1000 \text{ nm}^2$  by 2020, where only about ten NCs can be contained per memory cell. For such small scale, it becomes increasing challenging to synthesize suitable materials with uniform size and shape, and assemble them into a well-ordered NC matrix. In this letter, we present an approach to fabricate flash memory device with Co-SiO<sub>2</sub> core-shell NCs as charge storage nodes in the floating gate, where the Co-SiO<sub>2</sub> core-shell NCs are synthesized by biochemical technique to achieve controlled shape and size.

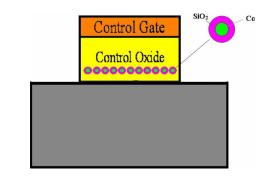

The NC memory device with Co–SiO<sub>2</sub> NC floating gate were fabricated on P-type silicon (100) substrate with the resistivity about 1–10  $\Omega$  cm. A schematic structure is shown in Fig. 1. After standard RCA clean and dilute 1:40 HF etch, thermal SiO<sub>2</sub> (~2 nm) was grown on silicon substrate at 850 °C. Our solution-phase synthesis of colloidal NCs is based on standard airless techniques on a Schlenk line.<sup>16,17</sup> First, cobalt NCs were fabricated by using a standard airless technique. As precursor for cobalt, di-cobalt octacarbonyl [CO<sub>2</sub>(CO)<sub>8</sub>] was used. A solution of 0.54 g of CO<sub>2</sub>(CO)<sub>8</sub> diluted in 3 ml of anhydrous o-dichlorobenzene (DCB) was

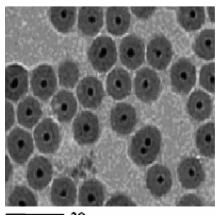

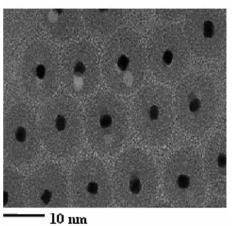

rapidly injected in a three-neck flask containing 0.1 g of tri-octylphosphine and 0.1 ml of oleic acid in refluxing DCB. The temperature of the solution was lowered after 5 min and the colloids were recovered using a gas-tight syringe. Second, the Co NCs were coated with SiO<sub>2</sub> by adding a 5 ml aliquot of 0.5 mg ml<sup>-1</sup> of synthesized colloids into a solution of 5 ml of Igepal CO-520 in 100 ml of cyclohexane. After this, a 0.6 ml solution of aqueous NH<sub>4</sub>OH was added dropwise, for subsequent addition of 0.5 ml of tetraethyl orthosilicate. This reaction proceeded for 48 h, after which the NCs were recovered by employing a solvent/antisolvent purification technique. This washing step included precipitation with excess hexane and collection by centrifugation, followed by redispersion in ethanol. Using the water-in-oil microemulsion technique, the NCs were synthesized with controlled shape and size, as shown in Fig. 2(a), where the diameter of cobalt core is about 3.4 nm and the SiO<sub>2</sub> shell thickness is about 3.5 nm. When self-assembled, separated by the insulating shell, the Co NCs can form a close pack with a density about  $\sim 0.8 \times 10^{12}$  cm<sup>-2</sup> on the tunneling oxide surface, as shown in Fig. 2(b), without aggregation. In our experiment, Co is more desirable as the core material compared to its semiconductor counterpart, such as Si or Ge, because metals have large work function and can be engineered down to 1 nm without decreasing potential well depth due to quantum confinement effects. Thus, continuous reduction of the shell thickness may yield ultrahigh density NC matrix, which can potentially satisfy long term requirements for nonvolatile memories as for ITRS 2007. After NCs were deposited, the wafer was annealed in N<sub>2</sub> at 500 °C for 10 min. Then about 20 nm low-pressure chemical vapor depo-

FIG. 1. (Color online) Schematic cross section view of  $Co-SiO_2$  memory cell.

<sup>&</sup>lt;sup>a)</sup>Electronic mail: liuhai@mail:utexas.edu.

20 nm (a)

(b)

FIG. 2. (a) Synthesized colloidal  $Co-SiO_2$  NCs. (b) Closely packed  $Co-SiO_2$  NCs.

sition  $SiO_2$  was deposited as control oxide and finally 2000 Å TaN was deposited by reactive dc sputtering at room temperature (RT) as control gate electrode. A control sample without Co-SiO<sub>2</sub> core-shell NCs but including all other layers was also fabricated to test the trapping characteristics of the dielectrics.

High frequency capacitance-voltage tests (1 MHz) were used to characterize the electrical properties of the devices. The threshold voltage ( $V_{th}$ ) was determined by applying a -3 to 3 V scan after each programing/erasing stress pulse.

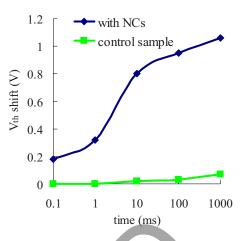

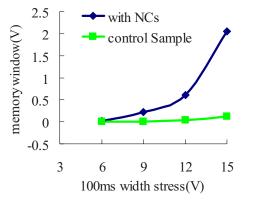

The programing characteristics as a function of voltage and pulse width for various operation conditions are shown

FIG. 4. (Color online) Programing speed for +15 V pulse.

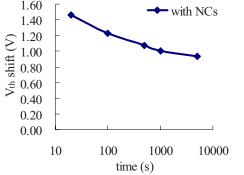

in Figs. 3 and 4, respectively. Figure 3 shows that the memory window, which is defined as the  $V_{th}$  difference between the programing and erasing state, increases with the stress pulse magnitude. About 2.0 V memory window can be observed under +15 V, 100 ms programing and -15 V, 100 ms erasing conditions. For programing speed characteristics, in Fig. 4,  $V_{th}$  shift about 0.8V can be obtained under +15 V, 10 ms stress. Meanwhile, for both cases, only negligible memory window was found for control sample. This indicates that stored charges are not due to the traps in bulk SiO<sub>2</sub> dielectric layer or the interface traps between control oxide and tunneling oxide, but due to the embedded NCs. By using the following equation, the electron storage number per NC can be calculated as

$$\Delta V_{\rm th} = \frac{q n_{\rm nc} x}{\varepsilon_{\rm ox}} \bigg( t_{\rm control} + 0.5 \frac{\varepsilon_{\rm ox} t_{\rm nc}}{\varepsilon_{\rm nc}} \bigg), \tag{1}$$

where the NC density  $n_{nc}=0.8 \times 10^{12}/\text{cm}^2$ , control oxide thickness  $t_{control}=20$  nm, tunneling oxide dielectric constant  $\varepsilon_{ox}(\text{SiO}_2)=3.9\varepsilon_0$ , and  $\varepsilon_{nc}$  is the dielectric constant of the NC. Since Co NC is used as charge storage nodes in our experiment,  $\varepsilon_{nc}$  is very large and the second term in the parenthesis can be neglected. From Fig. 4, V<sub>th</sub> shift under 15 V, 10 ms programing condition is about 0.8 V, thus it yields x=1.1 as the approximate number of electrons stored per NC.

Figure 5 shows the retention characteristics at RT. For an initial  $V_{th}$  shift about 1.52 V, about 0.88 V  $V_{th}$  shift still remains after 10<sup>4</sup> s. With extrapolation, 0.58 V  $V_{th}$  shift is still retained after 10<sup>8</sup> s. It is important to point out here that,

FIG. 3. (Color online) Memory window for different programing/erasing

This aroptions with 199tms pulse width in the article. Reuse of AIP content is subject to the EIG 5 (Color online) Retention characteristics at RT ownloaded to IP:

203112-3 Liu et al.

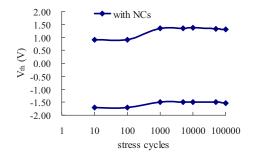

FIG. 6. (Color online) Endurance characteristics for  $\pm 15$  V, 100 ms stress cycles.

with the SiO<sub>2</sub> shell, the thermal stability of the metal core can be improved to reduce oxidation of cobalt NCs during annealing and control oxide deposition steps and promotes a better interface. Some previous research has also shown that this kind oxidation of the metal NCs, which degrades interface quality, is a major reason for poor retention characteristics.<sup>18</sup> The endurance characteristics can also benefit from the improvement of the interface quality, as shown in Fig. 6. After up to  $10^5$  program/erase cycles with ±15 V, 100 ms pulse, the memory window does not show obvious degradation.

In summary, we have presented a NC flash memory device using  $Co-SiO_2$  core-shell NCs as charge storage node in the floating gate. By using biochemical technique,  $Co-SiO_2$  NCs can be synthesized with controlled shape and size and closely packed to achieve high density. The insulating shell also can help to increase the thermal stability of the NC metal core during the fabrication process to improve the memory device performance.

This work was supported in part by DARPA, MARCO, and the Micro Foundation, as well as the NSF, NNIN program.

- <sup>1</sup>S. Tiwari, F. Rana, H. Hanafi, E. F. Crabbe, and K. Chan, Appl. Phys. Lett. **68**, 1377 (1996).

- <sup>2</sup>L. Kim, H. Han, H. Kim, J. Lee, B. Choi, S. Hwang, D. Ahn, and H. Shin, Proceedings of International Electron Device Meeting, 1998 (unpublished), p. 111.

- <sup>3</sup>C. Li, S. John, E. Quinones, and S. Banerjee, J. Vac. Sci. Technol. A 14, 170 (1996).

- <sup>4</sup>J. H. Chen, Y. Q. Wang, W. J. Yoo, Y. Yeo, G. Samudra, D. S. H. Chan, A. Du, and D. L. Kwong, IEEE Trans. Electron Devices **51**, 1840 (2004).

- <sup>5</sup>D.-W. Kim, T. Kim, and S. K. Banerjee, IEEE Trans. Electron Devices **50**, 1823 (2003).

- <sup>6</sup>J. J. Lee and D. L. Kwong, IEEE Trans. Electron Devices **52**, 507 (2005).

- <sup>7</sup>Z. Liu, C. Lee, V. Narayanan, G. Pei, and E. C. Kan, IEEE Trans. Electron Devices **49**, 1606 (2002).

- <sup>8</sup>Z. Liu, C. Lee, V. Narayanan, G. Pei, and E. C. Kan, IEEE Trans. Electron Devices **49**, 1614 (2002).

- <sup>9</sup>M. L. Ostraat, J. W. De Blauwe, M. L. Green, L. D. Bell, H. A. Atwater, and R. C. Flagan, J. Electrochem. Soc. **148**, G265 (2001).

- <sup>10</sup>M. Park, P. M. Chatkin, R. A. Register, and D. H. Adamson, Appl. Phys. Lett. **79**, 257 (2001).

- <sup>11</sup>K. W. Guarini, C. T. Black, Y. Zhang, I. V. Babich, E. M. Sikorski, and L. M. Gignac, Tech. Dig. Int. Electron Devices Meet. **2003**, 541.

- <sup>12</sup>P. V. Braun, P. Osenar, M. Twardowski, G. N. Tew, and S. I. Stupp, Adv. Funct. Mater. **15**, 1745 (2005).

- <sup>13</sup>D. Shahrjerdi, D. I. Garcia-Gutierrez, and S. K. Banerjee, IEEE Electron Device Lett. 28, 793 (2007).

- <sup>4</sup>S. Tang, C. Mao, Y. Liu, D. Q. Kelly, and S. K. Banerjee, IEEE Trans. Electron Devices **54**, 433 (2007).

- <sup>5</sup>International Technology Roadmap for Semiconductors (ITRS), 2007 edition.

- <sup>16</sup>D. C. Lee, F. V. Mikulec, J. M. Pelaez, K. Kool, and B. A. Korgel, J. Phys. Chem. B **110**, 20906 (2006).

- <sup>17</sup>A. T. Heitsch, D. K. Smith, R. N. Pate, D. Ress, and B. A. Korgel, J. Solid State Chem. **181**, 1590 (2008).

- <sup>18</sup>S. Ryu, J. Lee, J. Han, S. Kim, and Y. Choi, IEEE Trans. Electron Devices 56, 377 (2009).