# TiSi<sub>2</sub> Selective Growth in a Rapid Thermal Low Pressure Chemical Vapor Deposition System

## A. Bouteville and J. C. Remy

Laboratoire P.C.M.T., Universite d'Angers, Angers, France

## C. Attuyt

JIPELEC Company, Grenoble, France

#### ABSTRACT

The aim of this work is to selectively deposit titanium disilicide films on silicon area vs. silicon oxide area through a new commercial RTLPCVD apparatus. As a preliminary study, we tested our deposition system by using the well-known polysilicon deposition process. By this way, we showed that the temperature homogeneity on a 4 in. wafer is quite satisfying, and that the growth rates are about ten times higher than those obtained by using a standard hot wall LPCVD system. Then, we studied the titanium silicide deposition from either pure titanium tetrachloride or hydrogen-diluted titanium tetrachloride. As-deposited layers are well-adherent to the substrate and crystallized according to the C 54 structure. The resistivity ranges from 15-20  $\mu\Omega$ -cm and the selectivity on 8  $\mu$ m wide lines never fails. An anomalous substrate silicon etching is observed when pure titanium chloride is used but we show that hydrogen dilution inhibits this unwanted phenomenon. Chemical reactions are proposed to explain the silicide deposition and the unwanted formation of gaseous silicon species leading to this anomalous silicon etching when pure titanium chloride is used.

The decrease in transistor size in very large scale integrated (VLSI) circuits has made it necessary to consider new materials, new processes, and new deposition systems. For example, silicides, especially Ti, Ta, W, and Mo silicides, constitute one class of materials which are suitable as supplement or replacement for polysilicon to reduce the interconnection resistance<sup>1</sup>. The studies of these new materials lead to new processes. For example, the selectivity of growth is of great interest because several etching and lithography steps are suppressed<sup>2,3</sup>. Among the different deposition methods used in microelectronic technologies, chemical vapor deposition (CVD), with its advantages of good conformal coverage, high throughput, purity, possibility of selective deposition promises to be one of the best methods for depositing films in VLSI technologies so new deposition systems are developed. For example, rapid thermal processing has recently emerged to add new possibilities to traditional thermal techniques<sup>3,5</sup>

In a previous paper, we reported the possibility of obtaining, through a home-built low-pressure CVD system, the growth of titanium disilicide films on naked silicon surfaces while surrounding oxide regions remain free of any deposit<sup>6</sup>. The purpose of this study is first, to evaluate the performances of a commercial LPCVD system equipped with IR lamps, called rapid thermal LPCVD, then, by using this RTLPCVD system, to deposit selective titanium silicide films.

For any VLSI process involving heat-treatment, it is essential that the temperature be uniform and repeatable across the active surface area of the wafer. Even with the technological sophistication of all today's equipment, tools that can actually measure temperature uniformity are still lacking. This problem becomes crucial in a small cold-wall reactor where the temperature gradient is very high (about 300°C/cm). To map the wafer temperature, we chose a wellknown process; the polysilicon deposition. The wafer temperature is controlled through a pyrometrical measure at the center of the wafer. By measuring the thickness of deposited polysilicon at the center of the wafer, the deduced growth rate can be assigned to a true temperature value. By repeating polysilicon depositions at different temperatures of the wafer-center, a curve can be established between the growth rate and the true temperature value. After that, by mapping the thickness of the deposited polysilicon on the whole wafer, we can deduce the growth rate at every point of the wafer, then, by using the previously established curve, the true temperature can be mapped on the whole wafer.

This study is then divided in two parts. First, we established a temperature homogeneity on a 4 in. wafer. Secondly, once the temperature uniformity of the wafer was checked, we studied the selective deposition of titanium silicide on silicon vs. silicon dioxide through pure titanium tetrachloride or through hydrogen-diluted titanium tetrachloride.

### **Experimental Procedure**

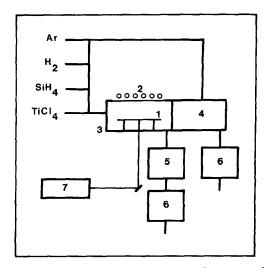

A schematic diagram of the commercial RTLPCVD system used is shown in Fig. 1. The reactor is designed for a 100 mm diam wafer. The former is heated by a tungsten infrared lamps array through two quartz plates separated by a cooling water flow. An infrared pyrometer measures the wafer temperature at the back-side center. The substrate temperature response is very high so it used to switch on and off the deposition process. Lateral and bottom walls are made of reflective stainless steel and are water-cooled to avoid thermal memory effects. The system is equipped with a loading chamber under vacuum. Before each run, the reactor is evacuated by a 80 l/s turbomolecular pump which is backed by a 12 m<sup>3</sup>/h mechanical pump. The system base pressure is about  $2 \times 10^{-5}$  Pa. During the process, only

Fig. 1. Diagram of the RTLPCVD system: 1. Si substrate; 2. Infrared lamps; 3. Water cooled walls; 4. Load lock; 5. Turbomolecular pump; 6. Mechanical pump; and 7. Optical pyrometer.

J. Electrochem. Soc., Vol. 139, No. 8, August 1992 © The Electrochemical Society, Inc.

Downloaded on 2015-03-24 to IP 169.230.243.252 address. Redistribution subject to ECS terms of use (see ecsdl.org/site/terms\_use) unless CC License in place (see abstract).

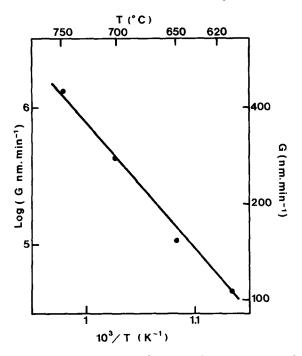

Fig. 2. Logarithm of the polysilicon growth rate (G) against the reciprocal absolute temperature.

the mechanical pump is used. The total pressure is measured by a capacitance gauge and kept constant by a controlled Ar flow injected between the reactor and the pump.

For the study of the temperature homogeneity through polysilicon deposition, 100 nm thermal oxide covered silicon wafers are used. The oxide layer on the substrate back side is removed by a local chemical etching (10/1 BHF). Pure silane is used at a flow rate of 10 sccm/min. The total pressure is fixed at 33 Pa. The investigated temperature range is between 600 to 750°C. Depending on the deposition temperature, the deposition duration is ranged from 10-40 s.

For the study of the selective titanium silicide deposition, the substrates are <100> oriented silicon wafers covered by a 100 nm thick thermal oxide layer which is then patterned in parallel stripes, alternating oxide (7 µm) and silicon windows (8 µm). The back-side oxide is not removed. Because of the selectivity of the titanium silicide deposition, the wafer back side is then kept free of any deposit and the pyrometrical measure is not disturbed. The temperature is fixed at 800°C. Liquid titanium tetrachloride is used. It is contained in a reservoir maintained at a constant temperature and connected to the reaction chamber via a metering valve. TiCl<sub>4</sub> flow rate is a function of the reservoir temperature, the reactor pressure, and the metering valve adjustment. No carrier gas is used. In all the experiments, the TiCl<sub>4</sub> flow rate is fixed at 20 mg/min. When pure titanium chloride is used, the total pressure is fixed at 34 Pa. Some experiments are carried out by adding a hydrogen flow rate of 100 sccm/min. In this case, the total pressure is fixed at 70 Pa. The deposition duration is fixed at 40 s.

#### **Results and Discussion**

Temperature homogeneity-polysilicon deposition.—The first result is that, in the entire range of deposition temper-

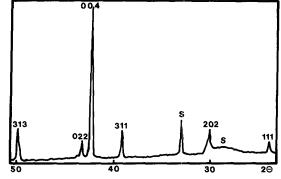

Fig. 3. X-ray diffraction spectrum of a as-deposited TiSi<sub>2</sub> film.

ature, the growth rates are very high. The obtained values are about ten times higher than those obtained through a standard hot wall LPCVD system. The logarithm of these growth rate values is plotted in Fig. 2 *vs.* the reciprocal absolute temperature. The apparent activation energy is about 0.86 eV. This value is lower than the activation energy of the silicon deposition process limited by the surface reaction (about 1.5 eV)<sup>7</sup>. So we can assume that the deposition process is limited by the mass transport rate of the silicon material to the wafer surface. This result could be expected because of the very high growth rate values obtained.

In Fig. 2, the growth rate of the polysilicon is deduced from thickness measurements performed at the wafer center which is just where the temperature is controlled during the deposition. So, the indicated temperature values are quite the true temperature values. Now, for a silicon deposit obtained at a fixed temperature of the wafer center, if we map the deposited silicon thickness, we can map the temperature on the entire 4 in. wafer by assigning to each deposited silicon thickness value, the corresponding growth rate value and then, by using Fig. 2, the true temperature value. On Table I, we can see the maximum variation of the thickness ( $\Delta t$ ), then the maximum variation of the growth rate ( $\Delta G$ ), then the maximum variation of the temperature ( $\Delta T$ ), for three temperature values of the wafer center: 650, 700, and 750°C, during a silicon deposition process of 39, 22, and 15 s, respectively, corresponding to a deposited silicon thickness of 110, 107, and 115 nm, respectively at the wafer center. As it can be seen in the last column, the temperature uniformity on the entire  ${\bf 4}$  in. wafer is better than 1%. The  $\Delta T/T$  values are quite comparable to the thermocouple accuracy.

Selective titanium disilicide.—In a previous paper<sup>6</sup>, we showed the possibility of obtaining selective deposition of titanium disilicide on naked silicon against silicon oxide adjacent surfaces by using an experimental LPCVD apparatus (consisting of a resistively heated 5 cm diam quartz tube). So, we carried on our experiments by studying the selective deposition of titanium silicide through the RTLPCVD system just tested through the preliminary silicon deposition study.

As-deposited films are always well-adherent to the substrate according to standard scotch tape test. X-ray diffraction analysis shows a polycrystalline structure according to the stable orthorhombic C 54 phase. A (004) preferred orientation can be observed in Fig. 3. The surface

| Table I. Tem | perature | variations | deduced | from    | Fia. | 2          |

|--------------|----------|------------|---------|---------|------|------------|

| Tuble I. Tem | peruitie | varianons  | acancea | ii Oili | ııy. | <b>*</b> . |

| Temperature<br>T(°C) | Thickness<br>t(nm) | Duration<br>(s) | $\Delta t^*$ (nm) | Growth rate<br>G(nm/min) | $\Delta G$ (nm/min) | Δ <i>T</i><br>(°C)  | $\Delta T/T \ \%$ |

|----------------------|--------------------|-----------------|-------------------|--------------------------|---------------------|---------------------|-------------------|

| 650<br>700<br>750    | 110<br>107<br>115  | 39<br>22<br>15  | 6.4<br>6.3<br>6.7 | $169\\293\\460$          | 10<br>17<br>27      | $4.5 \\ 4.5 \\ 6.0$ | 0.7<br>0.6<br>0.8 |

(\*Calculated from measurements at 15 mm from the wafer edge and the wafer center).

2261

Downloaded on 2015-03-24 to IP 169.230.243.252 address. Redistribution subject to ECS terms of use (see ecsdl.org/site/terms\_use) unless CC License in place (see abstract).

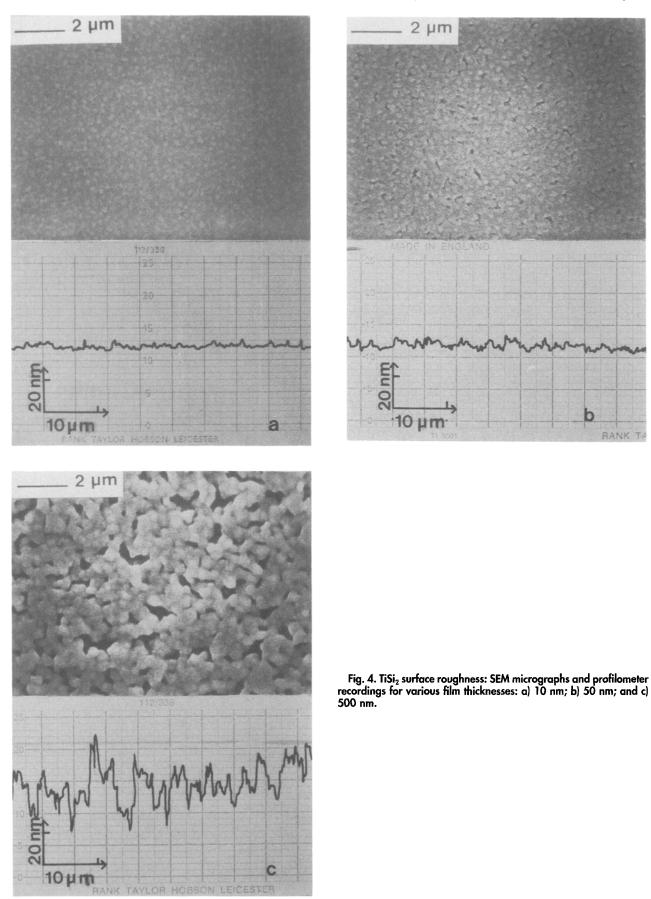

is observed by scanning electron microscopy (SEM) and checked by profilometry measurements. As it can be seen in Fig. 4, the roughness of the surface slowly increases with the thickness of the deposited film. Nevertheless, the "peak to peak" roughness remains below 30 nm for a 500 nm thick film. The resistivity, determined by using a four-point probe, ranges from 15 to 20  $\mu\Omega$ -cm which is quite consistent with the literature<sup>8</sup>. As expected with this RTLPCVD deposition system, the titanium silicide growth rate is very high: 800 nm/min when pure titanium chloride is used as

J. Electrochem. Soc., Vol. 139, No. 8, August 1992 C The Electrochemical Society, Inc.

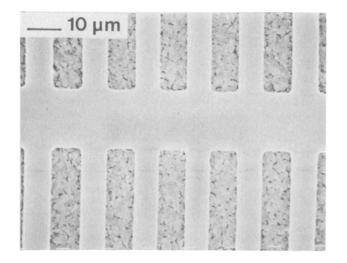

Fig. 5. SEM micrograph showing the strict selectivity of the TiSi<sub>2</sub> deposit.

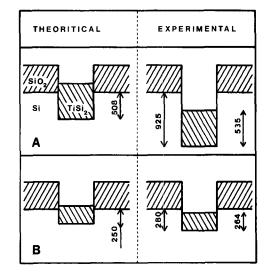

starting gaseous phase and 400 nm/min when hydrogen-diluted titanium chloride is used. In spite of these high growth rates, the selectivity never fails as it can be seen on SEM micrograph (Fig. 5). No encroachment phenomenon can be detected but an anomalous sinking of the silicide film in the silicon substrate can be revealed for titanium silicide films deposited from pure titanium chloride. According to the silicon and titanium disilicide densities, the formation of a 100 nm thick TiSi<sub>2</sub> film on top of a silicon wafer must lead to a 95 nm silicon consumption. Then, for a 535 nm thick TiSi<sub>2</sub> film, a silicon consumption of 508 nm can be expected. Actually, thickness measurements, using a stylus profilometer, show a 390 nm sinking, which corresponds to a true silicon consumption of 925 nm (Fig. 6). In fact, the difference between theoretical and experimental consumptions can be explained as a substrate etching leading to gaseous silicon by-products. To avoid this phenomenon, hydrogen is added to the starting gaseous phase. Thus, for a TiSi<sub>2</sub> 264 nm thick film (which involves a silicon consumption of 250 nm), we just observe a slight sinking of 16 nm corresponding to a 30 nm silicon etching. On the basis of a model proposed by Regolini et al.<sup>9</sup>, and according to our just mentioned experimental results, we can assume the following chemical reactions.

When pure titanium chloride is used as starting gaseous phase

$[TiCl_4] + 1.03 < Si > \rightarrow 0.28 < TiSi_2 > + 0.72 [TiCl_3] + 0.46 [SiCl_4]$

When hydrogen-diluted titanium chloride is used

$[\text{TiCl}_4] + 0.46 \langle \text{Si} \rangle + 1.2[\text{H}_2] \rightarrow 0.2 \langle \text{TiSi}_2 \rangle$

+  $0.8[\text{TiCl}_2] + 0.05[\text{SiH}_2\text{Cl}_2] + [\text{HCl}]$

From these reactions, a conversion rate, Y, of silicon to silicide can be calculated. For pure titanium chloride:  $Y_1 =$  $(0.28 \times 2)/1.03 = 0.54$ ; for hydrogen-diluted titanium chloride:  $Y_2 = (0.2 \times 2)/0.46 = 0.87$ .

Hence, in the pure titanium chloride case, 46% of consumed silicon disappear as gaseous silicon chloride and only 54% are converted into silicide. In the hydrogen-diluted titanium chloride case, the yield,  $Y_2$ , is as good as 87%.

#### Summary

In this paper, we study the selective deposition of titanium silicide films in a RTLPCVD system. From a preliminary work, we exhibit the very good temperature homogeneity and high growth rates. Then, disilicide titanium

Fig. 6. TiSi<sub>2</sub> formation (deposition duration: 40 s): A: by using pure TiCl<sub>4</sub> as starting gaseous phase; TiSi<sub>2</sub> thickness: 535 nm; unwanted silicon etching: 925 - 508 = 417 nm. B: by using hydrogen-diluted TiCl<sub>4</sub> as starting gaseous phase; TiSi<sub>2</sub> thickness: 264 nm; unwanted silicon etching: 280-250 = 30 nm.

films are deposited with a strict selectivity on 8 µm wide lines. An anomalous etching of the silicon substrate is observed when pure titanium chloride is used as starting gaseous phase. We show that this unwanted silicon etching can almost be suppressed by using hydrogen-diluted titanium chloride. In order to totally overcome the substrate consumption, we are carrying on experimentations by using TiCl<sub>4</sub>-SiH<sub>4</sub>-H<sub>2</sub> gaseous phase. Further results will be published.

### Acknowledgments

The authors would like to thank Dr. D. Bensahel, Dr. J. L. Regolini, and Dr. J. Mercier for their encouragement and helpful discussions.

Manuscript submitted April 20, 1990; revised manuscript received April 10, 1992.

The Universite D'Angers assisted in meeting the publication costs of this article.

#### REFERENCES

- 1. S. P. Murarka, Silicides for VLSI Applications, Academic Press, New York (1983).

- 2. K. C. Saraswat, S. Swirhun, and J. P. McVittie, in VLSI Science and Technology, K. E. Bean and G. A. Rozgonyi, Editors, PV 84-7, p. 409, The Electrochemi-cal Society Softbound Proceedings Series, Penning-

- ton, NJ (1984). 3. Y. Pauleau, in The Physics and Fabrication of Microstructures and Microdevices, C. Weisbuch and M. J. Kelly, Editors, p. 94, Springer-Verlag, New York (1983)

- 4. S. R. Wilson, W. M. Paulson, and R. B. Gregory, Solid State Technol., 28, 185 (1985)

- S. S. Chen, S. Sivaram, and R. K. Shukla, J. Vac. Sci. Technol., B5, 1750 (1987).

- 6. A. Bouteville, A. Royer, and J. C. Remy, This Journal, 134, 2080 (1987). 7. A. Kermani, K. E. Johnsgard, and F. Wong, *Solid State*

- Technol., **34,** 71 (1991).

- 8. V. Ilderem and R. Reif, This Journal, 135, 2590 (1988).

- 9. J. L. Regolini, D. Bensahel, G. Bomchil, and J. Mercier, Proceedings of The European Workshop on Refractory Metals and Silicides, p. 408, Applied Surface Science (1989).