## Study of dry oxidation of triangleshaped silicon nanostructure

J. L. Liu, Y. Shi, F. Wang, Y. Lu, S. L. Gu, R. Zhang, and Y. D. Zheng

Citation: Applied Physics Letters **69**, 1761 (1996); doi: 10.1063/1.117477 View online: http://dx.doi.org/10.1063/1.117477 View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/69/12?ver=pdfcov Published by the AIP Publishing

## Articles you may be interested in

Laser direct writing of oxide structures on hydrogenpassivated silicon surfaces Appl. Phys. Lett. **69**, 3013 (1996); 10.1063/1.116823

Characterization of largearea arrays of nanoscale Si tips fabricated using thermal oxidation and wet etching of Si pillars J. Vac. Sci. Technol. B **14**, 3420 (1996); 10.1116/1.588773

A triangleshaped nanoscale metal–oxide–semiconductor device J. Vac. Sci. Technol. B **14**, 4042 (1996); 10.1116/1.588640

Fabrication of nanostructures on silicon surfaces on wafer scale by controlling selforganization processes J. Vac. Sci. Technol. B **14**, 4134 (1996); 10.1116/1.588606

Formation of rareearth oxide doped silicon by spark processing Appl. Phys. Lett. **68**, 3416 (1996); 10.1063/1.115778

## Study of dry oxidation of triangle-shaped silicon nanostructure

J. L. Liu,<sup>a)</sup> Y. Shi, F. Wang, Y. Lu, S. L. Gu, R. Zhang, and Y. D. Zheng Department of Physics and Institute of Solid State Physics, Nanjing University, Nanjing 210093, People's Republic of China

(Received 22 January 1996; accepted for publication 8 July 1996)

Silicon nanostructures along [011] direction with upside down triangle cross sections on the top of the sawtooth structure with (111) facets are prepared by using the lithography technique, reactive ion etching, and anisotropic wet chemical etching. These triangle-shaped silicon nanostructures are thermally oxidized in dry oxygen over a range of temperature from 850 to 1000 °C, which is characterized by scanning electron microscopy. The self-limiting oxidation phenomenon observed in silicon nanostructures is discussed. Cross-sectional shape change of the silicon nanostructure under different oxidation temperatures is demonstrated. A silicon quantum wire is successfully fabricated by two-step thermal oxidation of the silicon nanostructures. © *1996 American Institute of Physics.* [S0003-6951(96)03038-0]

The thermal oxidation of the silicon is one of the most important processes in silicon industry. Historically, silicon dioxide generated by thermal oxidation played an important role in the development of both metal-oxide-semiconductors (MOS) and bipolar technology. As the ultralarge scale integration (ULSI) dimension approaches the nanoscale, the interest in the fabrication of silicon quantum wires with different shape contained within SiO<sub>2</sub> is increasing dramatically due to potential device application and novel physical phenomena.<sup>1,2</sup> This kind of silicon quantum wire has many remarkable advantages, for example, silicon quantum wires are produced with controllable lateral dimensions by precisely controlling the thermal oxidation process; electron or holes are completely confined since the wide-band-gap SiO<sub>2</sub> acts as a high potential barrier. This study of thermal oxidation characteristics of the silicon nanostructure is very important.

There have been many studies of the oxidation of silicon nanowires in recent years.<sup>3-6</sup> Most of these silicon nanostructures submitted to oxidation had cylindrical shape as discussed in these reports, and little work is being done on another shape of silicon wires such as triangle-shaped nanostructures, which have been considered as a novel nanostructure for realizing silicon quantum wires and other basic physical studies.<sup>7,8</sup> Recently, we reported the success of fabrication of silicon nanostructures with upside-down triangle cross sections on the top of the sawtooth structure by anisotropic wet chemical etching and realization of silicon quantum wires on the base of these triangle-shaped silicon nanostructure. It is found that the thermal oxidation is one of the critical process in fabricating silicon quantum wires, which not only form high-quality SiO2/Si interfaces, but also smooth and reduce the lateral dimensions of silicon quantum wires.<sup>8</sup> In this letter, we mainly study the thermal oxidation characteristics of the triangle-shaped silicon nanostructure. Dry oxidations of these structures are performed over a range of temperature from 850 to 1000 °C. Excellent results observed by using the scanning electron microscopy (SEM) are demonstrated. A silicon quantum wire is successfully fabricated.

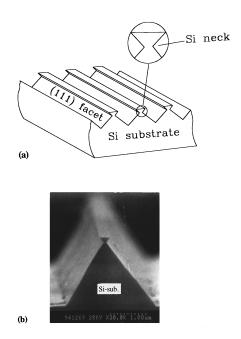

Figure 1(a) shows a schematic of the silicon nanostructure fabricated in this work. The starting material is a nominally on-axis p-type Si(100) wafer. First, thermal oxidation technique is carried out to grow a 100 nm SiO<sub>2</sub> layer which acts as a mask for anisotropic wet chemical etching. Then, line-and-space patterns along the [011] direction are formed by lithography technique. Next, 350-nm-deep trenches are generated in the substrate by using reactive ion etching. After removing the photoresist, the substrate is dipped in the anisotropic etchant using ethylendiominestrong pyrocatechol-water solutions<sup>9</sup> to form an upside down triangle cross section on the top of the sawtooth structure with (111) facets. Finally, the nanostructure is dipped in an aqueous HF solution for several minutes to remove the SiO<sub>2</sub> mask, as shown in Fig. 1(a). A cross-sectional image of SEM of as-etched nanostructure is shown in Fig. 1(b).

FIG. 1. (a) Schematic of silicon nanostructure fabricated in this work, and (b) SEM image of cross section of the unoxidized silicon nanostructure.

Appl. Phys. Lett. 69 (12), 16 September 1996

<sup>&</sup>lt;sup>a)</sup>Electronic mail: ydzheng@netra.nju.edu.cn

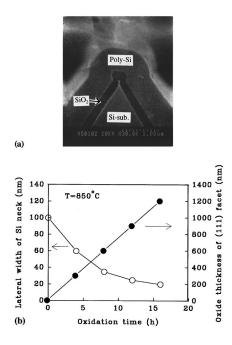

FIG. 2. (a) Cross-sectional SEM image of silicon nanostructure oxidized in dry oxygen at 850 °C for 10 h. (b) Typical 850 °C oxidation time progression of the lateral dimensions of silicon neck, and the oxide thickness of (111) plane on silicon substrate by anisotropic wet chemical etching.

A set of samples subjected to dry oxidation at different temperatures for different time periods were prepared under the same etching conditions to minimize Si nanostructure variations among the samples. The typical starting lateral dimensions of the neck region and the upper side of the silicon nanostructure are about 100 nm, 270 nm, respectively. All dimensional data are obtained from the micrograph of SEM. Figure 2(a) shows a cross-sectional image of SEM of silicon nanostructure oxidized at 850 °C for 10 h. In order to clearly observe the oxide morphology, the oxidized samples had a polycrystalline silicon mask deposited on them by very low pressure chemical vapor deposition (VLP/CVD),<sup>10</sup> and then were back-side polished and cleaved. The cleaved faces were delineative etched with an aqueous HF for several minutes. The space vacated by the oxide appears as a dark strip sandwiched between two bright areas of silicon and polycrystalline silicon. All the SEM specimen of the oxidized samples described in this letter were prepared by this preparation technique. By analyzing the oxide thicknesses at different portions in Fig. 2(a), it was found that the oxidation rate of triangle-shaped silicon nanostructures is faster than that of the silicon in the neck region and lower than that of (111) plane on patterned silicon substrate (sawtooth structure). Figure 2(b) shows typical 850 °C oxidation time progression of the lateral dimensions of the silicon neck and the oxide thickness of (111) plane on the silicon substrate. As the oxidation progresses, the planar field oxide thickness continues to increase linearly with the time while the silicon necks decrease slightly. Moreover, all the necks are nonvanishing and self-limit to 20 nm after 16 h oxidation. The retardation of oxidation is usually attributed to the additional stress from nonplanar viscous deformation of oxide.<sup>4</sup> In the thermal oxidation of silicon, the new oxide is formed at the Si-SiO<sub>2</sub> interface. Because the volume of an

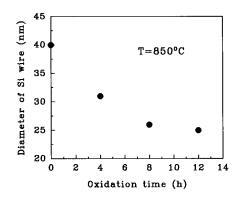

FIG. 3. 850 °C oxidation time progression of the diameters of silicon wires. The starting materials with initial diameter 40 nm are oxidized samples after 4 h oxidation at 1000 °C.

oxide molecule is about two times that of a silicon atom, volume expansion is necessary in the formation of the new oxide. Owing to very high viscosity of oxide, nonplanar twodimensional viscous deformation of the oxide produces large additional stress perpendicular to the Si-SiO<sub>2</sub> interface, this normal viscous stress makes the oxidation at the surface of silicon necks more difficult. They are two likely mechanisms for slowing down the oxidation rate of silicon neck region. One is that the surface reaction coefficient  $K_s$  is reduced by the normal viscous stress at the  $Si-SiO_2$  interface due to nonplanar viscous deformation of oxide.<sup>3,4</sup> Another is that oxygen diffusion is limited in a highly stressed oxide.<sup>5,11</sup> It has been noted that the limiting value in the present oxidation is larger than that (about 10 nm) reported in Ref. 11. The difference between them is not known, but the type of silicon is obviously a factor. In addition, the thickness of the oxide also plays an important role. Furthermore, the triangle shape is retained even though the sample is oxidized 16 h and the dimension is reduced to a very small value. This phenomenon does not occur when the sample is subjected to 1000 °C oxidation. After 4 h oxidation at 1000 °C, the silicon wires are isolated from the substrate and the triangle shape transfers to quasicircular shape. When the oxidation time is prolonged to 6 h, the silicon wires disappear. These results seem interesting, and it can also be understood by considering the effect of viscous stress in the oxide on the oxidation rate described above. At 850 °C or lower, no obvious change in the triangle structure occurs is due to the existence of viscous stress in the region of the two bottom angles of the triangle structure during oxide growth. At 1000 °C or higher, because there is a viscous flow of oxide to relieve the stress, the shape change and silicon wire isolation during oxidation are observed.

Figure 3(a) shows 850 °C oxidation time progression of the diameters of silicon wires. The starting materials with the initial diameter 40 nm are oxidized samples after 4 h oxidation at 1000 °C. As the oxidation progresses, it is found that the retardation of oxidation becomes obvious when the radius of the silicon wires is decreased. The retardation of oxidation is more pronounced compared to that of the silicon necks, and the wires self-limit to 25 nm here. This is because the oxide round the silicon wire is thicker than that round the silicon necks, and the curvature is sharper than that of silicon

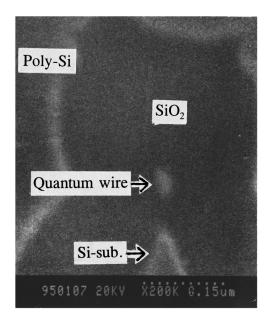

FIG. 4. Cross-sectional SEM image of a silicon quantum wire prepared by two-step thermal oxidation.

necks, thus leading to larger additional stress to make the oxidation more difficult.

We have presented some thermal oxidation characteristics of triangle-shaped silicon nanostructures, which may be very useful for realizing silicon quantum wires. The advantage of using dry thermal oxidation of cylindrical silicon nanostructures to fabricate silicon quantum wires has been demonstrated.<sup>2,5</sup> It was seen as an opportunity for fabricating high-quality silicon quantum wires with  $\pm 1$  nm control in lateral dimensions in the self-limiting regime of oxidation temperatures below 950 °C.5,11 For the present triangleshaped silicon nanostructures, oxidation at low temperatures (below 850 °C) is not practical because the silicon wires cannot be electrically isolated from the substrate due to the selflimiting effect as described above. In addition, though oxidation of the triangle-shaped silicon nanostructure at high temperatures (1000 °C or higher) can make the silicon wire isolated from the substrate and reduce the lateral dimension of it to form silicon quantum wire, we cannot precisely control the lateral dimensions of silicon quantum wires due to the impossibility of precisely selecting the time and temperature of oxidation process. Most important of all, surface roughness caused by dry etching and chemical wet etching is retained, which is harmful to device application.<sup>6,11</sup> Fortunately, we can obtain silicon quantum wires by using a twostep thermal oxidation process. High-temperature (1000 °C) oxidation for some time is used to isolate the silicon wires from the substrate and reduce the lateral dimension, then the silicon wires are oxidized below 850 °C to smooth the surface of the silicon wire to form the expected silicon quantum wires with uniform lateral dimensions. Figure 4 presents the cross-sectional SEM image of a silicon quantum wire with a quasicircular cross-sectional shape embedded in the SiO<sub>2</sub> layer. It is fabricated by first oxidizing at 1000 °C for 4 h, then the mid-temperature (850 °C) process of the thermal oxidation is used. The diameter of the silicon quantum wire is 25 nm.

In conclusion, we have successfully studied the dry oxidation of the triangle-shaped silicon nanostructures fabricated by lithography, reactive ion etching, and anisotropic etching. The time progression of the silicon wire reduction and the neck region oxide growth at low temperature (850 °C) indicates that after a few hours of oxidation both become extremely slow compared to the oxide growth rate of (111) facet of patterned sawtooth substrate. The self-limiting oxidation effect occurs at the temperatures below 850 °C. The cross-sectional shape change of silicon nanostructure under different oxidation temperatures is demonstrated. Excellent results are evidenced by SEM images. A silicon quantum wire is fabricated by two-step thermal oxidation in this way.

The authors would like to acknowledge D. A. Du and C. Y. Lin of the Center for Materials Analysis at Nanjing University for SEM measurement. This work was supported by the Chinese National High-Technology R&D Program, Chinese National Basic Science Program, and Chinese National Basic Science Foundation.

- <sup>1</sup>H. I. Smith and H. G. Craighead, Phys. Today **20**, 24 (1990).

- <sup>2</sup>Y. Nakajima, Y. Takahashi, S. Horiguchi, K. Iwadate, H. Namatsu, K. Kuihara, and M. Tabe, Appl. Phys. Lett. 65, 2833 (1994).

- <sup>3</sup>D. B. Kao, J. P. McVittie, W. D. Nix, and K. C. Saraswat, IEEE Trans. Electron Devices **ED-34**, 1008 (1987).

- <sup>4</sup>D. B. Kao, J. P. McVittie, W. D. Nix, and K. C. Saraswat, IEEE Trans. Electron Devices **ED-35**, 25 (1988).

- <sup>5</sup>H. L. Liu, D. K. Biegelsen, F. A. Ponce, N. M. Johnson, and R. F. W. Pease, Appl. Phys. Lett. **64**, 1383 (1994).

- <sup>6</sup>J. L. Liu, Y. Shi, F. Wang, Y. Lu, S. L. Gu, R. Zhang, and Y. D. Zheng, Appl. Phys. Lett. **68**, 352 (1996).

- <sup>7</sup>K. Morimoto, Y. Hirui, K. Yuld, M. Niwa, and J. Yasui, *Extended Abstracts of the 24th Conference on Solid State Devices and Materials, Hakabari* (Business Center for Academic Societies Japan, Tokyo, 1993), p. 344.

- <sup>8</sup>J. L. Liu, Y. Shi, F. Wang, R. Zhang, P. Han, B. H. Mao, and Y. D. Zheng, J. Vac. Sci. Technol. B **13**, 2137 (1995).

- <sup>9</sup>A. Reisman, M. Berkanblit, S. A. Chan, F. B. Kaufman, and D. C. Green, J. Electrochem. Soc. **126**, 1406 (1979).

- <sup>10</sup> Y. D. Zheng, R. Zhang, L. Q. Hu, S. L. Gu, R. L. Jiang, R. H. Wang, and P. Han, Mater. Res. Soc. Symp. Proc. **263**, 227 (1992).

- <sup>11</sup> H. L. Liu, D. K. Biegelsen, N. M. Johnson, F. A. Johnson, and R. F. W. Pease, J. Vac. Sci. Technol. B **11**, 2532 (1993).